# MIPS® Architecture Extension: nanoMIPS32™ DSP Technical Reference Manual

Revision 0.04 April 27, 2018 Public Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Tech, LLC, a Wave Computing company ("MIPS") and MIPS' affiliates as applicable. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or MIPS' affiliates as applicable or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS (AND MIPS' AFFILIATES AS APPLICABLE) reserve the right to change the information contained in this document to improve function, design or otherwise.

MIPS and MIPS' affiliates do not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS II, MIPS IV, MIPS V, MIPSr3, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS-VERIFIED, Aptiv logo, microAptiv logo, interAptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, proAptiv logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, 1074K, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, Navigator, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD-3, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS and MIPS' affiliates as applicable in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

# Contents

| Chapter 1: About This Book                                | 2  |

|-----------------------------------------------------------|----|

| 1.1: Typographical Conventions                            |    |

| 1.1.1: Italic Text                                        | 2  |

| 1.1.2: Bold Text                                          | 2  |

| 1.1.3: Courier Text                                       | 2  |

| 1.2: UNPREDICTABLE and UNDEFINED                          | 2  |

| 1.2.1: UNPREDICTABLE                                      |    |

| 1.2.2: UNDEFINED                                          |    |

| 1.2.3: UNSTABLE                                           |    |

| 1.3: Special Symbols in Pseudocode Notation               |    |

| 1.4: Notation for Register Field Accessibility            | 7  |

| 1.5: For More Information                                 | 9  |

|                                                           |    |

| Chapter 2: Guide to the Instruction Set                   |    |

| 2.1: Understanding the Instruction Fields                 | 10 |

| 2.1.1: Instruction Fields                                 |    |

| 2.1.2: Instruction Descriptive Name and Mnemonic          |    |

| 2.1.3: Format Field                                       |    |

| 2.1.4: Purpose Field                                      |    |

| 2.1.5: Description Field                                  |    |

| 2.1.6: Restrictions Field                                 |    |

| 2.1.7: Availability and Compatibility Fields              |    |

| 2.1.8: Operation Field                                    |    |

| 2.1.9: Exceptions Field                                   |    |

| 2.1.10: Programming Notes and Implementation Notes Fields |    |

| 2.2: Operation Section Notation and Functions             |    |

| 2.2.1: Instruction Execution Ordering                     |    |

| 2.2.2: Pseudocode Functions                               |    |

| 2.3: Op and Function Subfield Notation                    |    |

| 2.4: FPU Instructions                                     |    |

|                                                           |    |

# Chapter 3: The nanoMIPS® DSP Application Specific Extension to the nanoMIPS32® Architecture 30

| 3.1: Base Architecture Requirements                                       |  |

|---------------------------------------------------------------------------|--|

| 3.2: Compliance and Subsetting                                            |  |

| 3.3: Introduction to the nanoMIPS® DSP Module                             |  |

| 3.4: DSP Applications and their Requirements                              |  |

| 3.5: Fixed-Point Data Types                                               |  |

| 3.6: Saturating Math                                                      |  |

| 3.7: Conventions Used in the Instruction Mnemonics                        |  |

| 3.8: Effect of Endian-ness on Register SIMD Data                          |  |

| 3.9: Additional Register State for the DSP Module                         |  |

| 3.10: Software Detection of the DSP Module                                |  |

| 3.11: Exception Table for the DSP Module                                  |  |

| 3.12: DSP Module Instructions that Read and Write the DSPControl Register |  |

| 3.13: Arithmetic Exceptions                                               |  |

|                                                                           |  |

| apter 4: nanoMIPS® DSP Module Instruction Summary |   |

|---------------------------------------------------|---|

| 4.1: The nanoMIPS® DSP Module Instruction Summary |   |

| enter El la charactica. Encondita a               |   |

| apter 5: Instruction Encoding                     |   |

| 5.1: Instruction Bit Encoding                     |   |

| apter 6: The MIPS® DSP Module Instruction Set     | 5 |

| 6.1: Compliance and Subsetting                    |   |

| 6.2: DSP Module Specific Pseudocode Functions     |   |

|                                                   |   |

| 6.2.1: ValidateAccessToDSPResources()             |   |

| 6.2.2: ValidateAccessToDSP2Resources()            |   |

| ABSQ_S.PH                                         |   |

| ABSQ_S.QB.                                        |   |

| ABSQ_S.W.                                         |   |

| ADDQ[_S].PH                                       |   |

| ADDQ_S.W                                          |   |

| ADDQH[_R].PH                                      |   |

| ADDQH[_R].W                                       |   |

| ADDSC                                             |   |

| ADDU[_S].PH                                       |   |

| ADDU[_S].QB                                       |   |

| ADDWC                                             |   |

| ADDUH[_R].QB                                      |   |

| BALIGN                                            |   |

| BITREV                                            |   |

| BPOSGE32C                                         |   |

| CMP.cond.PH                                       |   |

| CMPGDU.cond.QB                                    |   |

| CMPGU.cond.QB                                     |   |

| CMPU.cond.QB                                      |   |

| DPA.W.PH                                          |   |

| DPAQ_S.W.PH                                       |   |

| DPAQ SA.L.W                                       |   |

| DPAQX S.W.PH                                      |   |

| DPAQX SA.W.PH                                     |   |

| DPAU.H.QBL                                        |   |

| DPAU.H.QBR                                        |   |

| DPAX.W.PH                                         |   |

| DPS.W.PH.                                         |   |

| DPSQ S.W.PH                                       |   |

| DPSQ_SA.L.W                                       |   |

| DPSQX S.W.PH                                      |   |

| DPSQX_SA.W.PH                                     |   |

| DPSU.H.QBL                                        |   |

| DPSU.H.QBR                                        |   |

| DPSX.W.PH                                         |   |

|                                                   |   |

| EXTP                                              |   |

| EXTPDP                                            |   |

| EXTPDPV                                           |   |

| EXTPV                                             |   |

| EXTR[_RS].W                                       |   |

| EXTR_S.H.                                         |   |

| EXTRV[_RS].W                                      |   |

| EXTRV S.H          | 144 |

|--------------------|-----|

| INSV.              |     |

| LBUX               |     |

|                    |     |

| LWX                |     |

| MADD               |     |

|                    |     |

| MADDU              |     |

| MAQ_S[A].W.PHL     |     |

| MAQ_S[A].W.PHR     |     |

| MFHI               |     |

| MFLO               |     |

| MODSUB             |     |

| MSUB               | 168 |

| MSUBU              | 170 |

| MTHI               | 172 |

| MTHLIP             | 174 |

| MTLO               | 176 |

| MUL S].PH          |     |

| MULEQ S.W.PHL      |     |

| MULEQ S.W.PHR      |     |

| MULEU S.PH.QBL     |     |

| MULEU S.PH.QBR.    |     |

| MULQ RS.PH         |     |

| MULQ_RS.W          |     |

|                    |     |

| MULQ_S.PH.         |     |

| MULQ_S.W           |     |

| MULSA.W.PH.        |     |

| MULSAQ_S.W.PH      |     |

| MULT               |     |

| MULTU              |     |

| PACKRL.PH          |     |

| PICK.PH            |     |

| PICK.QB.           |     |

| PRECEQ.W.PHL       | 210 |

| PRECEQ.W.PHR       | 212 |

| PRECEQU.PH.QBL     | 214 |

| PRECEQU.PH.QBLA    | 216 |

| PRECEQU.PH.QBR     |     |

| PRECEQU.PH.QBRA    |     |

| PRECEU.PH.QBL      |     |

| PRECEU.PH.QBLA     |     |

| PRECEU.PH.QBR.     |     |

| PRECEU.PH.QBRA     |     |

|                    |     |

| PRECR.QB.PH        |     |

| PRECR_SRA[_R].PH.W |     |

| PRECRQ.PH.W.       |     |

| PRECRQ.QB.PH.      |     |

| PRECRQU_S.QB.PH    |     |

| PRECRQ_RS.PH.W.    |     |

| PREPEND            |     |

| RADDU.W.QB         | 244 |

| RDDSP              |     |

| REPL.PH            | 248 |

| REPL.QB                                                                   |  |

|---------------------------------------------------------------------------|--|

| REPLV.PH                                                                  |  |

| REPLV.QB                                                                  |  |

| SHILO                                                                     |  |

| SHILOV                                                                    |  |

| SHLL[_S].PH                                                               |  |

| SHLL.QB                                                                   |  |

| SHLLV[_S].PH                                                              |  |

| SHLLV.QB                                                                  |  |

| SHLLV_S.W                                                                 |  |

| SHLL_S.W                                                                  |  |

| SHRA[_R].QB                                                               |  |

| SHRA[_R].PH                                                               |  |

| SHRAV[_R].PH                                                              |  |

| SHRAV[_R].QB                                                              |  |

| SHRAV_R.W                                                                 |  |

| SHRA_R.W                                                                  |  |

| SHRL.PH                                                                   |  |

| SHRL.QB                                                                   |  |

| SHRLV.PH                                                                  |  |

| SHRLV.QB                                                                  |  |

| SUBQ[_S].PH                                                               |  |

| SUBQ_S.W                                                                  |  |

| SUBQH[_R].PH                                                              |  |

| SUBQH[_R].W                                                               |  |

| SUBU[_S].PH                                                               |  |

| SUBU[_S].QB                                                               |  |

| SUBUH[_R].QB                                                              |  |

| WRDSP                                                                     |  |

| Appendix A: Endian-Agnostic Reference to Register Elements                |  |

| A.1: Using Endian-Agnostic Instruction Names                              |  |

| A.2: Mapping Endian-Agnostic Instruction Names to DSP Module Instructions |  |

| Appendix B: Revision History                                              |  |

|                                                                           |  |

# **List of Figures**

| Figure 2.1: Example of Instruction Description                                                                                                          |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 2.2: Example of Instruction Fields                                                                                                               |            |

| Figure 2.3: Example of Instruction Descriptive Name and Mnemonic                                                                                        |            |

| Figure 2.4: Example of Instruction Format                                                                                                               |            |

| Figure 2.5: Example of Instruction Purpose                                                                                                              |            |

| Figure 2.6: Example of Instruction Description                                                                                                          |            |

| Figure 2.7: Example of Instruction Restrictions                                                                                                         |            |

| Figure 2.8: Example of Instruction Operation                                                                                                            |            |

| Figure 2.9: Example of Instruction Exception                                                                                                            | . 15       |

| Figure 2.10: Example of Instruction Programming Notes                                                                                                   |            |

| Figure 2.11: COP_LW Pseudocode Function                                                                                                                 |            |

| Figure 2.12: COP_LD Pseudocode Function                                                                                                                 |            |

| Figure 2.13: COP_SW Pseudocode Function                                                                                                                 |            |

| Figure 2.14: COP_SD Pseudocode Function                                                                                                                 |            |

| Figure 2.15: CoprocessorOperation Pseudocode Function                                                                                                   |            |

| Figure 2.16: MisalignedSupport Pseudocode Function                                                                                                      |            |

| Figure 2.17: AddressTranslation Pseudocode Function                                                                                                     |            |

| Figure 2.18: LoadMemory Pseudocode Function                                                                                                             |            |

| Figure 2.19: StoreMemory Pseudocode Function                                                                                                            |            |

| Figure 2.20: Prefetch Pseudocode Function                                                                                                               |            |

| Figure 2.21: SyncOperation Pseudocode Function                                                                                                          |            |

| Figure 2.22: ValueFPR Pseudocode Function                                                                                                               |            |

| Figure 2.23: StoreFPR Pseudocode Function                                                                                                               |            |

| Figure 2.24: CheckFPException Pseudocode Function                                                                                                       |            |

| Figure 2.25: FPConditionCode Pseudocode Function                                                                                                        |            |

| Figure 2.26: SetFPConditionCode Pseudocode Function                                                                                                     |            |

| Figure 2.27: Are64BitFPOperationsEnabled Pseudocode Function                                                                                            |            |

| Figure 2.28: IsCoprocessorEnabled PseudocodeFunction                                                                                                    | . 24       |

| Figure 2.29: IsCoprocessor2 Pseudocode Function                                                                                                         |            |

| Figure 2.30: IsEJTAGImplemented Pseudocode Function                                                                                                     |            |

| Figure 2.31: IsFloatingPointImplemented Pseudocode Function                                                                                             |            |

| Figure 2.32: sign_extend Pseudocode Functions                                                                                                           |            |

| Figure 2.33: memory_address Pseudocode Function                                                                                                         |            |

| Figure 2.34: Instruction Fetch Implicit memory_address Wrapping                                                                                         |            |

| Figure 2.35: AddressTranslation implicit memory_address Wrapping                                                                                        | . 27       |

| Figure 2.36: SignalException Pseudocode Function                                                                                                        |            |

| Figure 2.37: SignalDebugBreakpointException Pseudocode Function                                                                                         |            |

| Figure 2.38: SignalDebugModeBreakpointException Pseudocode Function                                                                                     |            |

| Figure 2.39: NullifyCurrentInstruction PseudoCode Function                                                                                              |            |

| Figure 2.40: PolyMult Pseudocode Function<br>Figure 3.1: Computing the Value of a Fixed-Point (Q7) Number                                               |            |

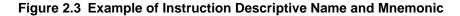

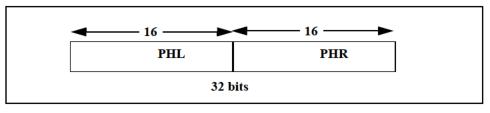

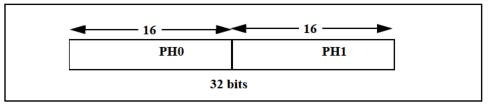

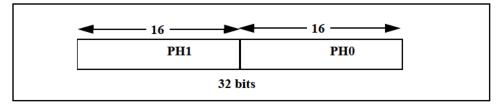

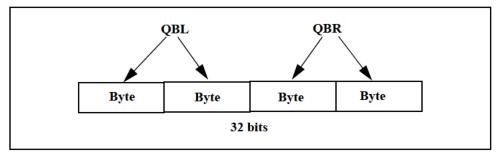

| Figure 3.1: Computing the value of a Fixed-Point (Q7) Number<br>Figure 3.2: A Paired-Half (PH) Representation in a GPR for the microMIPS32 Architecture | . 33<br>24 |

| Figure 3.2: A Paired-Hall (PH) Representation in a GPR for the microWIPS32 Architecture                                                                 |            |

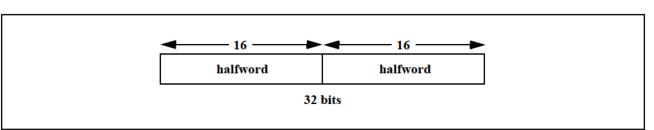

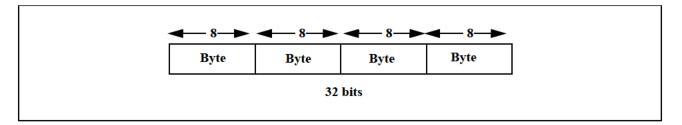

| Figure 3.3: A Quad-Byte (QB) Representation in a GPR for the hanomine 332 Architecture<br>Figure 3.4: Operation of MULQ_RS.PH rd, rs, rt                |            |

| Figure 3.5: MIPS® DSP Module Control Register (DSPControl) Format                                                                                       | 20.        |

| Figure 3.6: Config3 Register Format                                                                                                                     |            |

| Figure 3.7: CP0 Status Register Format                                                                                                                  |            |

| right of a status register i offici i sinthin international statements and the statement of the statement of the                                        | . 00       |

| Figure 6.1: ValidateAccessToDSPResource Pseudocode Function                                          | 58    |

|------------------------------------------------------------------------------------------------------|-------|

| Figure 6.2: ValidateAccessToDSP2Resources Pseudocode Function                                        | 59    |

| Figure 6.3: Operation of the INSV Instruction                                                        | . 146 |

| Figure A.1: The Endian-Independent PHL and PHR Elements in a GPR for the microMIPS32 Architecture    | . 309 |

| Figure A.2: The Big-Endian PH0 and PH1 Elements in a GPR for the microMIPS32 Architecture            | . 309 |

| Figure A.3: The Little-Endian PH0 and PH1 Elements in a GPR for the microMIPS32 Architecture         | . 309 |

| Figure A.4: The Endian-Independent QBL and QBR Elements in a GPR for the microMIPS32 Architecture    | . 310 |

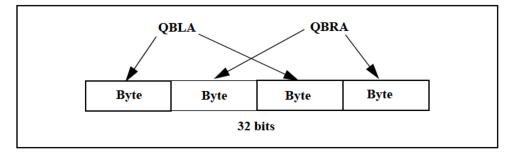

| Figure A.5: The Endian-Independent QBLA and QBRA Elements in a GPR for the microMIPS32 Architecture. | . 310 |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                                        | 4  |

|----------------------------------------------------------------------------------------------------|----|

| Table 1.2: Read/Write Register Field Notation                                                      |    |

| Table 2.1: AccessLength Specifications for Loads/Stores                                            | 20 |

| Table 3.1: Data Size of DSP Applications                                                           |    |

| Table 3.2: The Value of a Fixed-Point Q31 Number                                                   |    |

| Table 3.3: The Limits of Q15 and Q31 Representations                                               | 32 |

| Table 3.4: MIPS® DSP Module Control Register (DSPControl) Field Descriptions                       | 36 |

| Table 3.5: Instructions that set the ouflag bits in DSPControl                                     | 37 |

| Table 3.7: Exception Table for the DSP Module                                                      | 39 |

| Table 3.6: Cause Register ExcCode Field                                                            | 39 |

| Table 3.8: Instructions that Read/Write Fields in DSPControl                                       | 40 |

| Table 4.1: List of Instructions in nanoMIPS® DSP Module in Arithmetic Sub-class                    | 41 |

| Table 4.2: List of Instructions in nanoMIPS® DSP Module in GPR-Based Shift Sub-class               | 44 |

| Table 4.3: List of Instructions in nanoMIPS® DSP Module in Multiply Sub-class                      | 46 |

| Table 4.4: List of Instructions in MIPS® DSP Module in Bit/ Manipulation Sub-class                 | 51 |

| Table 4.5: List of Instructions in MIPS® DSP Module in Compare-Pick Sub-class                      | 51 |

| Table 4.6: List of Instructions in MIPS® DSP Module in Accumulator and DSPControl Access Sub-class | 53 |

| Table 4.7: List of Instructions in MIPS® DSP Module in Indexed-Load Sub-class                      |    |

| Table 4.8: List of Instructions in MIPS® DSP Module in Branch Sub-class                            | 56 |

| Table 5.1: Symbols Used in the Instruction Encoding Tables                                         | 57 |

|                                                                                                    |    |

# **Chapter 1**

# **About This Book**

This chapter describes the terminology and conventions for describing features of the MIPS<sup>®</sup> Architecture such as instructions and control and status registers.

# **1.1 Typographical Conventions**

This section describes the use of *italic*, **bold** and courier fonts in this book.

## 1.1.1 Italic Text

- is used for emphasis

- is used for *bits*, *fields*, and *registers* that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S* and *D*

- is used for the memory access types, such as cached and uncached

## 1.1.2 Bold Text

- represents a term that is being **defined**

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through 1

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

## 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

# **1.2 UNPREDICTABLE and UNDEFINED**

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

# **1.2.1 UNPREDICTABLE**

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

UNPREDICTABLE results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in another process

- UNPREDICTABLE operations must not halt or hang the processor

## **1.2.2 UNDEFINED**

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

## 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

UNSTABLE values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# **1.3 Special Symbols in Pseudocode Notation**

In this book, algorithmic descriptions of an operation are described using a high-level language pseudocode resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

| Symbol                                        | Meaning                                                                                                                                                                                                                                                           |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                             | Assignment                                                                                                                                                                                                                                                        |

| =,≠                                           | Tests for equality and inequality                                                                                                                                                                                                                                 |

|                                               | Bit string concatenation                                                                                                                                                                                                                                          |

| x <sup>y</sup>                                | A <i>y</i> -bit string formed by <i>y</i> copies of the single-bit value <i>x</i>                                                                                                                                                                                 |

| b#n                                           | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| 0bn                                           | A constant value <i>n</i> in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                              |

| 0xn                                           | A constant value $n$ in base 16. For instance $0x100$ represents the hexadecimal value 100 (decimal 256).                                                                                                                                                         |

| x <sub>y z</sub>                              | Selection of bits $y$ through $z$ of bit string $x$ . Little-endian bit notation (rightmost bit is 0) is used. If $y$ is less than $z$ , this expression is an empty (zero length) bit string.                                                                    |

| x.bit[y]                                      | Bit <i>y</i> of bitstring <i>x</i> . Alternative to the traditional MIPS notation $x_{y}$ .                                                                                                                                                                       |

| x.bits[yz]                                    | Selection of bits y through z of bit string x. Alternative to the traditional MIPS notation $x_{y z}$ .                                                                                                                                                           |

| x.byte[y]                                     | Byte <i>y</i> of bitstring <i>x</i> . Equivalent to the traditional MIPS notation $x_{8*y+7}$ $x_{8*y-7}$                                                                                                                                                         |

| x.bytes[yz]                                   | Selection of bytes y through z of bit string x. Alternative to the traditional MIPS notation $x_{8*y+7}$ $x_{8*z}$                                                                                                                                                |

| x halfword[y]<br>x.word[i]<br>x.doubleword[i] | Similar extraction of particular bitfields (used in e.g., MSA packed SIMD vectors).                                                                                                                                                                               |

| x.bit31, x.byte0, etc.                        | Examples of abbreviated form of x.bit[y], etc. notation, when y is a constant.                                                                                                                                                                                    |

| x fieldy                                      | Selection of a named subfield of bitstring <i>x</i> , typically a register or instruction encoding.<br>More formally described as "Field y of register x".<br>For example, FIR.D = "the D bit of the Coprocessor 1 Floating-point Implementation Register (FIR)". |

| +, -                                          | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                |

| *, ∞                                          | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                            |

| div                                           | 2's complement integer division                                                                                                                                                                                                                                   |

| mod                                           | 2's complement modulo                                                                                                                                                                                                                                             |

| /                                             | Floating point division                                                                                                                                                                                                                                           |

| <                                             | 2's complement less-than comparison                                                                                                                                                                                                                               |

| >                                             | 2's complement greater-than comparison                                                                                                                                                                                                                            |

| ≤                                             | 2's complement less-than or equal comparison                                                                                                                                                                                                                      |

| 2                                             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                   |

| nor                                           | Bitwise logical NOR                                                                                                                                                                                                                                               |

| xor                                           | Bitwise logical XOR                                                                                                                                                                                                                                               |

| and                                           | Bitwise logical AND                                                                                                                                                                                                                                               |

| or                                            | Bitwise logical OR                                                                                                                                                                                                                                                |

### Table 1.1 Symbols Used in Instruction Operation Statements

| Symbol        | Meaning                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| not           | Bitwise inversion                                                                                                                                                                                                                                                                                                                                                     |

| &&            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                                                                                                                             |

| <<            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                                                                                                                                |

| >>            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                                                                                                                                |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                                                                                    |

| GPR[x]        | CPU general-purpose register x. The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                                                                                             |

| SGPR[s,x]     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose registers may be implemented. <i>SGPR[s,x]</i> refers to GPR set <i>s</i> , register <i>x</i> .                                                                                                                                                                  |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                                                                                                     |

| FCC[CC]       | Floating Point condition code CC. <i>FCC[0]</i> has the same value as <i>COC[1]</i> .<br>Release 6 removes the floating point condition codes.                                                                                                                                                                                                                        |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register x                                                                                                                                                                                                                                                                                                               |

| CPR[z,x,s]    | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                                                                                      |

| CP2CPR[x]     | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                                                                         |

| CCR[z,x]      | Coprocessor unit <i>z</i> , control register <i>x</i>                                                                                                                                                                                                                                                                                                                 |

| CP2CCR[x]     | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                                                                         |

| COC[z]        | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                                                                                   |

| Xlat[x]       | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                                                                                      |

| BigEndianMem  | Endian mode as configured at chip reset ( $0 \rightarrow$ Little-Endian, $1 \rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions) and the endianness of Kernel and Supervisor mode execution.                                                                                  |

| BigEndianCPU  | The endianness for load and store instructions ( $0 \rightarrow$ Little-Endian, $1 \rightarrow$ Big-Endian). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).                                                                        |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as $(SR_{RE} \text{ and User mode})$ .                                                                                               |

| LLbit         | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions. |

# Table 1.1 Symbols Used in Instruction Operation Statements (Continued)

| Symbol                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  | Meaning                                                                                                                                                                                    |                      |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| I:,<br>I+n:,<br>I-n:              | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction labeled <b>I+1</b> appears to occur "at the same time" as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |                                  |                                                                                                                                                                                            |                      |

| PC                                | The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the instruc-<br>tion word. The address of the instruction that occurs during the next instruction time is determined by assign-<br>ing a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time by any<br>pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16e instruc-<br>tion) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during the<br>instruction time of the instruction in the branch delay slot.<br>In the MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the restart<br>address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an<br>exception. Release 6 adds PC-relative address computation and load instructions. The PC value contains a<br>full 32-bit address, all of which are significant during a memory reference.                                                                                                            |                                  |                                                                                                                                                                                            |                      |

| ISA Mode                          | In processors that implement the MIPS16e Application Specific Extension or the microMIPS base architec-<br>tures, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing, as fol-<br>lows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                                                                                                                                                                                            |                      |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Encoding                         | Meaning                                                                                                                                                                                    |                      |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                | The processor is executing 32-bit MIPS instructions                                                                                                                                        |                      |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                | The processor is executing MIIPS16e or microMIPS instructions                                                                                                                              |                      |

|                                   | In the MIPS Architecture, the <i>ISA Mode</i> value is only visible indirectly, such as when the processor stores a combined value of the upper bits of PC and the <i>ISA Mode</i> into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |                                                                                                                                                                                            |                      |

| PABITS                            | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{PABITS} = 2^{36}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |                                                                                                                                                                                            |                      |

| FP32RegistersMode                 | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). It is optional if the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |                                                                                                                                                                                            |                      |

|                                   | were a microMIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 implementanis bit is a 0, the | ave a compatibility mode in which the processor reference<br>tion. In such a case <b>FP32RegisterMode</b> is computed from<br>e processor operates as if it had 32, 32-bit FPRs. If this b | om the FR bit in the |

|                                   | The value of <b>FP32</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RegistersMod                     | le is computed from the FR bit in the <i>Status</i> register.                                                                                                                              |                      |

| InstructionInBranchDe-<br>laySlot | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |                                                                                                                                                                                            |                      |

# Table 1.1 Symbols Used in Instruction Operation Statements (Continued)

| Symbol                 | Meaning                                                                                                     |

|------------------------|-------------------------------------------------------------------------------------------------------------|

| SignalException(excep- | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument |

| tion, argument)        | parameter as an exception-specific argument). Control does not return from this pseudocode function-the     |

|                        | exception is signaled at the point of the call.                                                             |

# Table 1.1 Symbols Used in Instruction Operation Statements (Continued)

# 1.4 Notation for Register Field Accessibility

In this document, the read/write properties of register fields use the notations shown in Table 1.1.

| Read/Write<br>Notation | Hardware Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Software Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W                    | A field in which all bits are readable and writable by software and, potentially, by hardware.<br>Hardware updates of this field are visible by software read. Software updates of this field are visible by<br>hardware read.<br>If the Reset State of this field is "Undefined", either software or hardware must initialize the value before<br>the first read will return a predictable value. This should not be confused with the formal definition of<br><b>UNDEFINED</b> behavior.                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R                      | A field which is either static or is updated only by<br>hardware.<br>If the Reset State of this field is either "0", "Pre-<br>set", or "Externally Set", hardware initializes this<br>field to zero or to the appropriate state, respectively,<br>on powerup. The term "Preset" is used to suggest<br>that the processor establishes the appropriate state,<br>whereas the term "Externally Set" is used to sug-<br>gest that the state is established via an external<br>source (e.g., personality pins or initialization bit<br>stream). These terms are suggestions only, and are<br>not intended to act as a requirement on the imple-<br>mentation.<br>If the Reset State of this field is "Undefined", hard-<br>ware updates this field only under those conditions<br>specified in the description of the field. | A field to which the value written by software is<br>ignored by hardware. Software may write any value<br>to this field without affecting hardware behavior.<br>Software reads of this field return the last value<br>updated by hardware.<br>If the Reset State of this field is "Undefined", soft-<br>ware reads of this field result in an <b>UNPREDICT-</b><br><b>ABLE</b> value except after a hardware update done<br>under the conditions specified in the description of<br>the field. |

| Read/Write<br>Notation | Hardware Interpretation                                                                                                                                                                                               | Software Interpretation                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|