IP and Processors for Smart Edge Designs

A unified AI platform from the edge to the datacenter

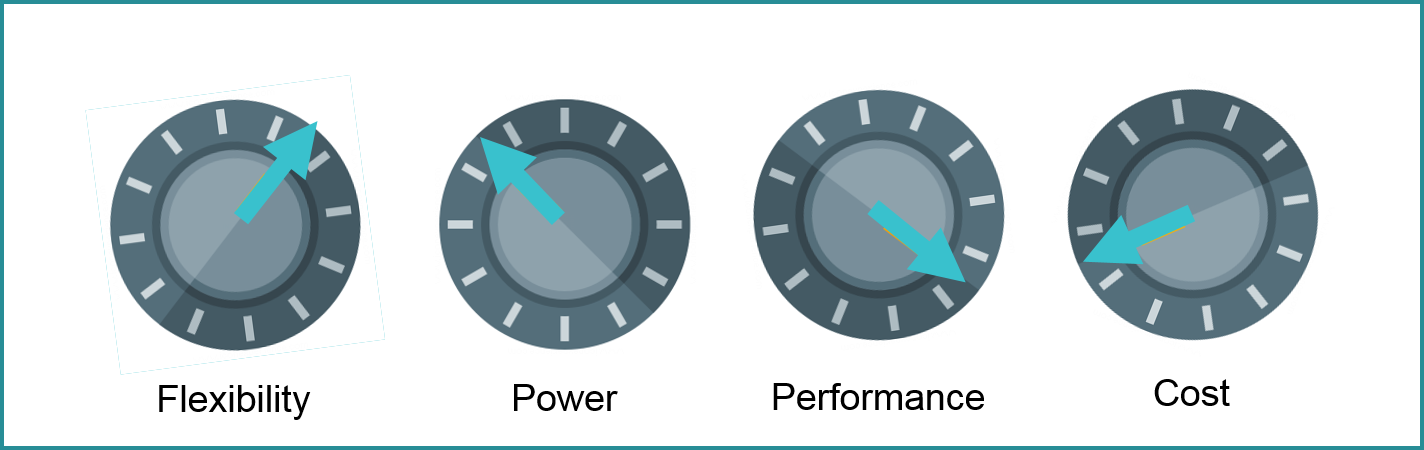

Wave’s AI IP platform features a unique combination of AI engines for achieving the right balance of flexibility, performance, efficiency and cost.

AI networks requiring low latency, high throughput, concurrent and efficient execution.

Multi-threaded, Multi-core, Multi-cluster CPUs, Multi-tile dataflow cores

Complete AI Technology Building Blocks

Sign Me Up for Early Access

At Wave, we’re always working on what’s next. Sign up to be the first to learn about and test our next generation designs.

MIPS Processor Cores

MIPS offers a comprehensive portfolio of low-power, high-performance 32- and 64-bit processor IP cores, ranging from high-end mobile applications processors to extremely small cores for deeply embedded microcontrollers.

M-Class Product Family

M-Class cores are ideal for micro-controller and embedded-type applications such as industrial controllers, Internet of Things (IoT), wearables, wireless communications, automotive and storage. M-Class line-up offers both micro-controller (MCU) and microprocessor (MPU) versions. One of the key features of the family includes hardware virtualization that provides a foundation for MIPS multi-domain security leading to the highest level of security for any embedded micro-controller architecture.

M51xx

DATASHEET

SOFTWARE MANUAL

MIPS32® M5100 Processor Core Family Software User’s Manual

MIPS32® M5150 Processor Core Family Software User’s Manual

OTHER DOCS

Using Virtualization to Implement a Scalable Trusted Execution Environment in Secure SoCs

Hardware-assisted Virtualization with the MIPS Virtualization Module

MIPS-VZ Security Features as Compared to ARMv8-M CMSE

M62xx

DATASHEET

PROGRAMMERS GUIDE

I-Class Product Family

MIPS 32-bit/64-bit I-Class cores are designed for the next generation of high-performance wireless communications, networking, automotive and AI applications. I-Class cores provide highly efficient, scalable, parallel processing performance, designed upon a foundation of hardware multi-threading and multi-core cluster CPU technologies. The latest MIPS I-class core also implements the I7200 nanoMIPS™ instruction set architecture (ISA), a new version of MIPS ISA designed to deliver best in class small code size without sacrificing performance.

I7200

MIPS I7200 Multiprocessing System Datasheet

MIPS I7200 Multiprocessing System Programmer’s Guide

I6500-F

I6500

I6400

P-Class Product Family

MIPS P-Class family, which ranges on the high-end of the MIPS performance spectrum, is being used for connected consumer electronics, supercomputer and HPC applications. The MIPS P-class CPU is based on a wide issue, deeply out-of-order (OoO) implementation, supporting up to six cores in a single cluster with high performance cache coherency. Complementing this raw horsepower, the P-Class family of cores includes a 128-bit integer and floating point SIMD processor, hardware virtualization, and larger physical and virtual addressing capabilities.

P-Class P5600

P5600 Multiprocessing System Datasheet

P5600 Multiprocessing System Software User’s Manual

P-Class P6600

MIPS Aptiv Cores

MIPS microAptiv is the smallest, lowest-power CPU family available. The microAptiv cores also have higher performance than competing converged microcontroller/DSP solutions in their class.

MIPS interAptiv is a family of multi-core, multi-threaded 32-bit processors. The MIPS interAptiv CPU family of processors gives designers access to two virtual processing elements (VPEs), or hardware threads, which appear as two complete processors within a symmetric multiprocessing (SMP) operating system.

proAptiv CPUs are based on a wide issue, deeply out-of-order (OoO) implementation of the MIPS32 architecture and are available in single or multi-core product versions supporting up to six cores.

microAptiv

DOWNLOAD microAptiv FAMILY BRIEF

DATASHEET

SOFTWARE MANUAL

MIPS32 microAptiv UP Processor Core Family Software Users Manual

MIPS32 microAptiv UC Processor Core Family Software Users Manual

OTHER DOCS

The Convergence of MCU/MPU and DSP

interAptiv

DOWNLOAD interAptiv FAMILY BRIEF

MIPS32® interAptiv Multiprocessing System Datasheet

MIPS32® interAptiv Multiprocessing System Software User’s Manual

proAptiv

DOWNLOAD proAptiv FAMILY BRIEF

MIPS Classic Cores

MIPS Classic Cores target every level of performance needed to support any embedded use case from entry-level to high-performance — whether it be digital consumer, broadband access and networking, or state-of-the-art communications.

DOWNLOAD MIPS CLASSIC CORES FAMILY BRIEF

MIPS32 1074Kc/f

DATASHEET

MIPS32® 1074K™ Coherent Processing System Datasheet

SOFTWARE

Boot-CPS: Example Example Boot Code for MIPS® Cores

MIPS32® 1074K™ CPU Family Software User’s Manual

MIPS32 1004Kc/f

DATASHEET

MIPS32® 1004K™ Coherent Processing System Datasheet

The MIPS32® 1004K™ Product Brief

SOFTWARE

MIPS32® 1004K™ CPU Family Software User’s Manual

Programming the MIPS32® 1004K™ Coherent Processing System Family

MIPS32 74Kc/f

DATASHEET

MIPS32® 74Kc™ Processor Core Datasheet

MIPS32® 74Kf™ Processor Core Datasheet

SOFTWARE

Programming the MIPS32® 74K® Core Family

Programming the MIPS® 74K® Core Family for DSP Applications

MIPS32® 74K® Processor Core Family Software User’s Manual

OTHER DOCS

Architectural Strengths of the MIPS32® 74K® Core Family

Breaking the Gigahertz Speed Barrier with an Automated Flow Using Synopsys ICC Compiler

MIPS32 34Kc/f

DATASHEET

MIPS32® 34Kc™ Processor Core Datasheet

MIPS32® 34Kf™ Processor Core Datasheet

SOFTWARE MANUAL

MIPS32® 34K™ Processor Core Family Software User’s Manual

OTHER DOCS

MIPS® MT Principles of Operation

Programming the MIPS32® 34K™ Core Family

MIPS32 24K

DATASHEET

MIPS32® 24Kc™ Processor Core Datasheet v4.00

MIPS32® 24Kf™ Processor Core Datasheet v4.00

SOFTWARE MANUAL

MIPS32® 24K® Processor Core Family Software User’s Manual v3.11

OTHER DOCS

Programming the MIPS32® 24K® Core Family v4.63

The MIPS32® 24KE™ Core Family: High-Performance RISC Cores with DSP Enhancements

Working with ScratchPad RAMs for MIPS32® 24K® and 34K® Cores

MIPS32 M14K/c

DATASHEET

MIPS32® M14K™ Processor Core data sheet

MIPS32® M14Kc™ Processor Core Family Datasheet

SOFTWARE MANUAL

MIPS32® M14K™ Processor Core Family Software User’s Manual

MIPS32® M14Kc™ Processor Core Family Software User’s Manual

MIPS32 M4K/4K

DATASHEET

MIPS32® M4K® Processor Core Data Sheet

SOFTWARE MANUAL

MIPS32® 4K® Processor Core Family Software User’s Manual

MIPS32® M4K® Processor Core Software User’s Manual

Contact Us

Want to accelerate your AI project with Wave innovation? Let us help you discover the power of our scalable dataflow technology.

LET’S CONNECTSign Me Up for Early Access

At Wave, we’re always working on what’s next. Sign up to be the first to learn about and test our next generation designs.

SIGN UP